2012年10月28日,由中国计算机学会主办的 “2012年全国高性能计算学术年会”(HPC China 2012)在湖南省张家界阳光酒店召开。本届盛会围绕着高性能计算技术的研究进展与发展趋势、高性能计算的重大应用等主题展开,促进信息化与工业化的深度融合,为相关领域的学者提供交流合作、发布最前沿科研成果的平台,推动中国高性能计算的发展。

在下午的分论坛中,中国科学院的杨佳先生为大家带来了《曙光6000全局集合通信芯片的可测试性设计与实现》。首先,他讲到D6000GSW集合通信芯片是大规模并行系统科学计算时,其通信模式中存有大量集合通信模式。

中国科科学院 杨佳

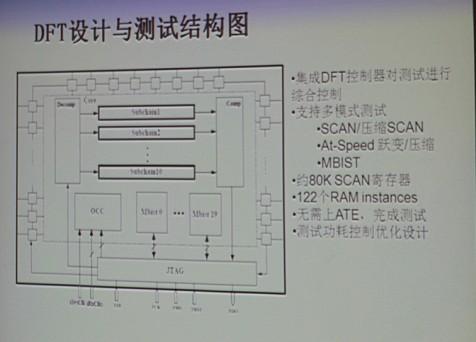

杨佳先生还介绍了D6000GSW芯片主要功能与规格,它支持集合通信操作,可靠全局同步,集成全局归约处理引擎:40X64bit ALU Array,支持Reduce,ALL-Reduce处理、80Gbps处理能力,还支持64bit证书、64bit双精度浮点数。

其中,扫描链设计采用多种SCAN模式,提高测试故障覆盖类型与覆盖率,支持Full SCAN/SCAN压缩,压缩比10:1,减少测试向总量,覆盖连接性故障,测试时采用慢速时钟。支持At-Speed跳变/压缩测试,测试时需TCK与系统工作时交替进入芯片。

在谈到At-Speed测试的时候,杨佳先生讲道,因At-Speed测试时芯片内部节点翻转率远大雨芯片正常工作模式,故新品峰值功耗会远大于正常工作时的功耗。

最后杨佳先生总结道,At-speed测试可以提高测试的故障覆盖类型,但应用时,需针对具体芯片结构采取相应的策略,以控制测试功耗的最大幅增加。片上DFT控制器(JTAG)的应用,大大简化了测试控制,使不以来ATE测试成为可能,同时,使测试成本大为缩减。