近日,NEO半导体拓展了3D X-DRAM概念,推出了新变体技术。这项技术以3D堆叠结构为核心理念,借鉴3D NAND闪存的经验,结合创新型单元结构和新材料的应用,旨在突破传统DRAM在密度、功耗与性能方面的技术瓶颈,对高性能计算(HPC)、人工智能(AI)以及高带宽存储(HBM)等前沿领域带来影响。

简单来说,它就相当于把一层楼的图书馆改装成了一座高楼大厦——同样大小的芯片,能存更多的数据,还能更快地调出用到的内容,如果能落地,直观来说,笔记本能玩的游戏更高级,体验更丝滑,AI训练更快,手机甚至可能拥有512GB内存。

什么是3D X-DRAM?

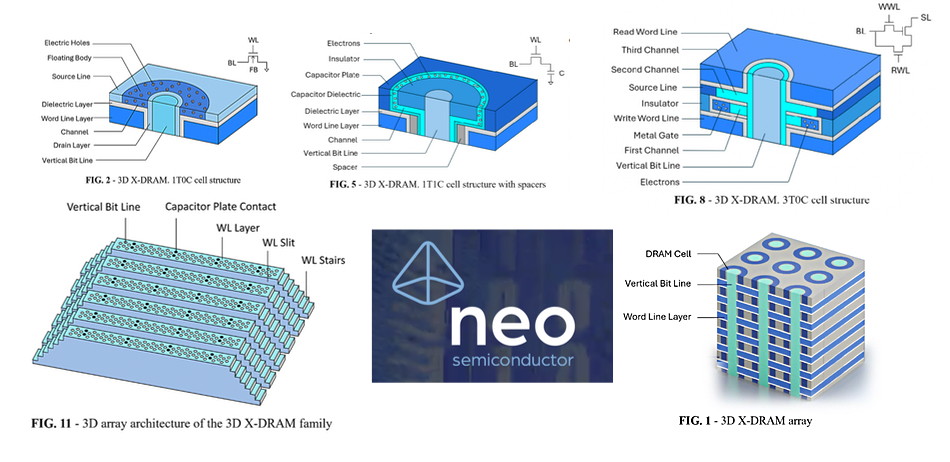

与传统平面型(2D)DRAM不同,NEO半导体的3D X-DRAM采用了垂直堆叠的方式,将存储单元结构在三维空间内展开。其核心思想是通过3D架构提升单位面积的存储密度,从而降低成本、提升带宽并优化能效比。

与以往依赖缩小电容器尺寸的2D DRAM路径不同,3D X-DRAM采用一种更具可持续性的演进路线,强调通过空间堆叠获得增长潜力,同时还能兼容现有的部分3D NAND制造工艺,具备更强的产业化落地可能性。

技术核心:从1T0C到1T1C和3T0C

3D X-DRAM最初构想是基于1T0C(单晶体管、零电容器)浮体单元结构,这种架构简化了制造流程,有助于提升堆叠密度。但为了适配更广泛应用需求,NEO半导体进一步发展出两个重要变体:

1T1C(单晶体管+电容器):引入高K电介质作为电容器,来延长数据保留时间,减少刷新频率,从而降低功耗。采用IGZO(氧化铟镓锌)材料作为沟道,提供更优的电气性能与制造一致性。NEO半导体表示,该结构可实现超过450秒的数据保留时间,远高于传统DRAM的毫秒级水准。

3T0C(三晶体管+零电容器):基于电流感应机制实现数据读写,省去电容器的设计,更适合高速、低延迟应用,如AI推理和存内计算等场景。这种结构特别强调高带宽和计算密度,为新一代计算架构提供可能。

制造工艺与堆叠密度

NEO半导体在阵列设计方面大量借鉴了3D NAND的成熟工艺。例如,字线采用“阶梯结构”引出、垂直位线设计、扇区化隔离布局等。这些设计不仅提升了访问效率,还增强了制造良率。

同时,NEO半导体正在研发支持512层堆叠结构,其目标是在单芯片内实现64Gb至512Gb的容量,相比目前0a节点的48Gb 2D DRAM,存储密度能提升10倍以上。这对AI模型训练、大数据处理等场景具有极大吸引力。

3D X-DRAM还特别针对AI、HPC等领域做出多项优化,比如,3D X-DRAM 用于高带宽内存(HBM),由于其更宽的总线宽度,它将具有更高的带宽。HBM3e支持1K比特位的总线宽度,预计2026年HBM4将达到2K位。相比之下,3D X-DRAM 独特的阵列结构以及支持混合键合技术,能将总线宽度扩展至4K比特位以上,最高可达32K比特位,带宽提升高达16倍,同时显著降低功耗和发热量,使其成为人工智能应用的变革性技术。

这些优势为未来AI芯片、图形加速器和数据中心存储带来颠覆式改变,有望取代部分HBM或成为其有力补充。

最后

当然,NEO半导体并非唯一关注3D DRAM的企业。三星、SK海力士和美光等都在推进三维化转型。比如三星正在研发VS-DRAM(垂直堆叠DRAM),其结构与NEO半导体的1T1C类似。

SK海力士曾披露面向未来HBM结构的3D DRAM实验计划,美光则聚焦于TSV优化与更低功耗HBM DRAM产品。

NEO半导体的不同之处在于其聚焦创新型单元结构(1T1C/3T0C)和最大限度地借用3D NAND生态,形成技术落地路径上的先发优势。

目前,NEO半导体的1T0C测试芯片正在开发中,1T1C测试芯片计划在2026年亮相。

尽管前路仍需解决制造工艺整合、成本控制与市场验证等挑战,但3D X-DRAM显然是打破当前DRAM密度瓶颈的一次重要尝试。这不仅是NEO半导体的技术突破,更是整个存储行业朝向三维化、异构集成和AI时代转型的缩影。