日立制作所和日本瑞萨科技面向闪存EEPROM,日前共同开发出了面积业界最小的内存单元。并在2003年12月8日于美国召开的“IEDM 2003”国际半导体制造技术会议上公布了技术详情。使用90nm最小加工尺寸时内存单元仅为0.016μm2(用F代表最小加工尺寸时单元面积为2F2)。顺便提一下,韩国三星电子同样在IEDM 2003上展示了4Gbit NAND型闪存,EEPROM内存单元面积采用70nm最小加工尺寸时则为0.025μm2。值得关注的是瑞萨科技的内存单元尽管使用的最小加工尺寸比三星的还大,但是面积却更小。

如果采用瑞萨科技的新内存单元,就能在约100mm2芯片面积中封装4Gbit容量。“目前已经使用这种内存单元试制出毫不逊色于实际产品的大容量内存阵列(Memory Array),并且已经证实写入时的数据传输速度可达到业界最快的10MB/秒”(瑞萨科技)。该公司将于2004年第3季度提供采用此次内存单元、容量4Gbit的用于保存数据的闪存EEPROM样品,2004年第4季度量产供货。还将向市场推出用于保存数据的容量2Gbit闪存EEPROM。定于2006年推向市场的8Gbit产品也将采用此次的内存单元。

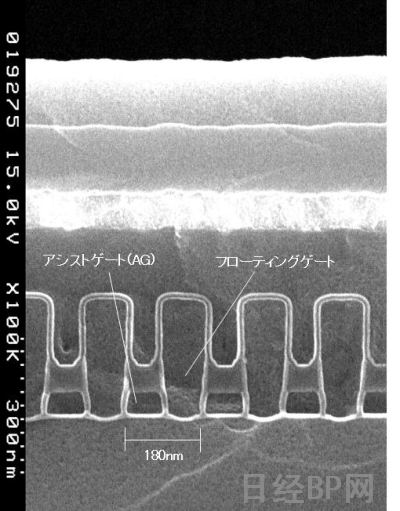

瑞萨科技此次开发的内存单元截面结构

瑞萨科技此次开发的内存阵列结构

利用反转层形成源极和漏极

此次开发的是瑞萨科技自主研制的第2代“AG(辅助栅)-AND”型多值(2bit/单元)内存单元。AG-AND型的单元结构是在单元内横向排列用于单元间元件分离的辅助栅和浮动栅。第1代AG-AND型内存单元已经被应用于该公司目前使用130nm最小加工尺寸进行量产的容量1Gbit、保存数据用闪存EEPROM中。

瑞萨科技此次之所以能够实现业界最小的内存单元面积,是因为从根本上彻底改进了单元晶体管的源极和漏极形成方法。该公司的原产品(第1代AG-AND型)在硅底板内注入离子、即利用扩散层形成单元晶体管的源极和漏极。在MOS晶体管的源极和漏极形成方法中是一种普通方法。但是由于扩散层本身需要一定的横向尺寸,因此每个bit的实际内存单元面积较大,为3F2。“扩散层本身的尺寸几乎等同于最小加工尺寸F。因此内存单元的短边长为2F,长边长度还要在短边上额外加上扩散层尺寸,所以就是3F。于是内存单元的物理面积就变成了6F2。由于在一个内存单元中多值保存2bit信息,因此每bit的实际内存单元面积就是3F2”(瑞萨科技)。

瑞萨科技在第2代AG-AND型内存单元中,利用反转层形成源极和漏极。反转层是指通过在栅极上加电,而在硅底板表面部分(数nm厚)生成高浓度电子区的手法。目前已经被应用于MOS晶体管沟道。由于反转层在单元内只形成于辅助栅正下方的底板表面上,因此本身不像扩散层那样需要横向尺寸。故而,每个bit的实际单元面积可做成2F2。

使用反转层后,源极和漏极的电阻就会增大,因此存在访问性能下降的问题。而瑞萨则通过优化井(well)浓度,确保了与第1代产品相同的性能。