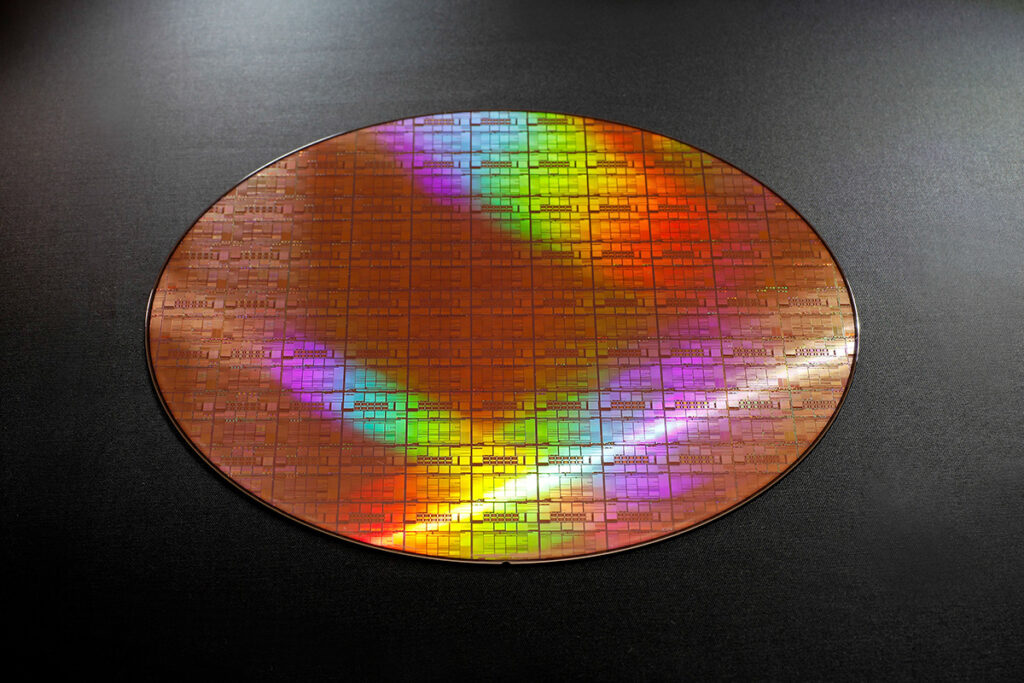

近期,日本芯片制造商 Rapidus 的 2nm 节点 2HP 引发业内的关注。据消息人士 Kurnal 表示,通过对 Rapidus 分享的数据进行拟合计算,其 2HP 工艺逻辑密度可达 237.31 MTr/mm²,与台积电同代制程 N2 的 236.17 MTr/mm² 几无差异,这一数据彰显了 Rapidus 的 2nm 制程在 PPA(Power 功耗、Performance 性能、Area 面积)三个角度之一的 Area(面积)端有着良好的表现。

然而,评估一个先进制程节点的综合水平,不能仅依靠逻辑密度这一项指标,Power(功耗)和 Performance(性能)数据同样至关重要。只有当这些数据全部出炉,才能对 Rapidus 2nm 工艺 2HP 的整体性能和能效做出准确判定。而且,良率和生产效率也是决定该制程节点能否在商业上取得成功的关键因素。

值得一提的是,由于英特尔在 Intel 18A 节点引入的 BSPDN 背面供电技术对芯片设计产生了改变,使得其逻辑密度无法与非 BSPDN 的2nm系列制程直接比较。这也凸显了不同厂商在技术路线选择和设计优化上的差异。

Rapidus已于今年7月完成了首块2nm GAA晶圆的试制,并制定了明确的量产目标,计划到 2027 年实现 25000 WPM(每月晶圆数量)规模的量产。此外,Rapidus 的 2nm PDK(工艺设计套件)预计将在 2026 年第一季度向客户提供。