PCIe(Peripheral Component Interconnect Express,外围组件互连)是高性能串行计算机扩展总线标准,广泛用于连接处理器与外围设备,如SSD、GPU和网卡等。

从发布以来,PCIe就凭借其高带宽、低延迟、向后兼容性强等特性,成为现代PC、服务器以及AI数据中心的主流连接方式。

PCIe 架构简述:点对点的串行通信机制

PCIe 并非传统的并行总线,而是采用点对点的串行链路结构,将CPU与外设之间以通道(lane)为单位建立连接。每个通道由一对接收线和一对发送线组成,支持双向传输。

根据设备需要,链路可以由1、2、4、8或16个通道组成,通道数量越多,总带宽越高。

PCIe 的数据传输以数据包的形式进行,每个数据包由包头和有效载荷组成。为避免复杂的同步机制,PCIe 使用嵌入式时钟,省去了传统并行总线所需的独立时钟线。

在物理层面,标准印刷电路板(PCB)上使用的FR-4材料支持约30厘米的链路长度,超出后通常需添加重定时器或中继器。

各代 PCIe 标准技术演进特征

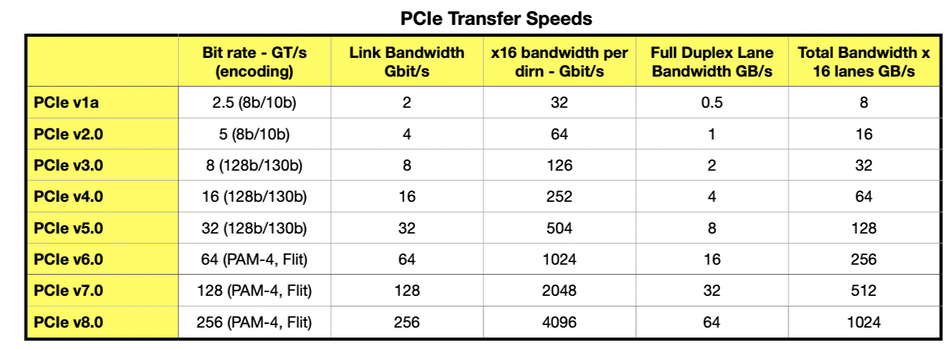

每一代PCIe标准的主要提升方向是提高每通道的传输速率,并优化编码方式降低协议开销。以下是PCIe各代标准关键特性的整理:

PCIe 3.0

• 编码方式:8b/10b(每8位数据需10位传输)

• 开销率:25%

• 每通道原始速率:8 GT/s(Giga Transfers per second)

• 每通道有效带宽:约1 GB/s

PCIe 4.0

• 传输速率:16 GT/s

• 编码升级:128b/130b(开销降至约1.6%)

• 每通道带宽:约1.97 GB/s

PCIe 5.0

• 传输速率:32 GT/s

• 带宽翻倍:约3.94 GB/s/通道

• 市场状态:广泛用于数据中心和高性能服务器

PCIe 6.0

• 传输技术重大变革:引入PAM4(4个电压电平),单次传输携带2位数据

• 传输速率:64 GT/s

• 关键机制:

• 引入 Flit(流量控制单元),固定256字节大小,用于增强高带宽稳定性

• 改变了数据打包机制,替代早期的可变长度TLP(事务层数据包)

• 每通道有效带宽:约7.88 GB/s

比如美光9650 Pro SSD已开始部署。

PCIe 7.0 与 8.0 的技术方向与预期性能

PCIe 7.0(预计2028年问世)

• 传输速率:128 GT/s,为PCIe 6.0的两倍

• 调制方式:延续PAM4

• 协议结构:继续使用Flit机制

• 链路优化:

• 可能支持基于光纤的互连形式

• 为满足HPC、超大规模数据中心、军工与汽车系统等场景的超高速需求而设计

• 典型应用:面向800G以太网、AI加速卡、大型GPU通信等极端带宽场景

规范发布后12~18个月内可能实现产业化,但不太可能快速进入主流PC消费市场

PCIe 8.0(标准制定中)

• 目标传输速率:256 GT/s(每通道256 Gbps)

• 可能采用新调制方式:

• PAM8(每次传输3比特)

• 或更高阶PAM16(每次传输4比特)

技术挑战:

• 铜缆在高频下的损耗问题可能难以解决

• 需借助光学墨水、电光混合互连、信噪比增强与高阶纠错机制等新型材料与技术

未来或达成每通道1 Tbps(等价125 GB/s)传输性能四、编码效率与信道设计的权衡演化

PCIe 发展过程中,提高单通道传输速率与优化编码效率始终是核心。早期版本因编码开销大,带宽利用率有限。后续标准逐步引入更高效的编码,如128b/130b,再引入PAM4等先进调制方案,以突破带宽瓶颈。

但调制精度提升也带来了电信号完整性、功耗、散热和接收端判决能力等方面的挑战。因此,从PCIe 6.0开始引入Flit机制,通过数据与控制统一打包、固定长度管理来降低传输误差与流控混乱,提高高频运行的可靠性。

发展节奏规律与未来趋势

从PCIe 4.0开始,标准迭代逐步进入“三年一更”的稳定节奏,每一代几乎都能实现带宽翻倍。未来随着AI大模型、边缘计算、8K视频、实时交互类应用高速增长,单通道TB级传输和光电混合连接将成为PCIe演进的重要方向。