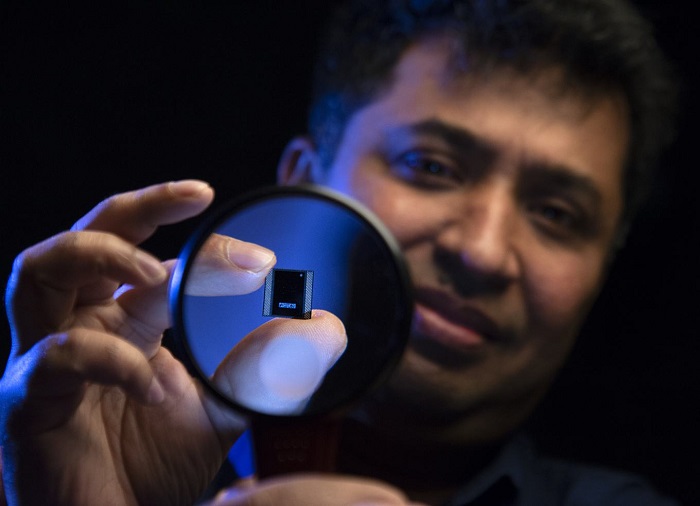

经历了漫长的等待和爆料,英特尔终于将公众的注意力吸引到了 Lakefield 芯片的本体上。如下图所示,该公司芯片工程事业部的 Wilfred Gomes,让我们看清了在放大镜背后的 Lakefield 芯片的样子。据悉,该系列处理器的亮点,在于采用了混合式设计 —— 包括一个大型的 Sunny Cove 内核(基于 10nm 制程),以及四个高效的 Tremont 内核(同样基于 10nm 工艺)。

(题图 via Hardwareluxx)

有趣的是,英特尔并未使用单芯片,而是为 Lakefield 处理器上运用了 3D 堆叠的设计,涵盖 CPU 内核、I/O、以及其它 IP 模块。

借助此前介绍过的 Foveros 封装技术,动态随机存储器(DRAM)可位于 Lakefield 芯片的顶层,且各个单独的组件可运用不同的工艺组合。

即便算上封装,Lakefield 处理器也只有五层,大小为 10×10 平方毫米,高度仅 1 毫米。

包括一个带有高速缓存和 I/O 控制器的基础芯片、单个 Sunny Cove 高性能内核 + 四个 Tremont 内核、Gen11 核显、内存控制器芯片、以及双层 DRAM(PoP 内存)。

英特尔宣称待机功率仅为 2 mW,负载状态下的表现暂不得而知。

首批采用 Lakefidle 处理器的设备包括微软 Surface Neo、三星 Galaxy Book S、以及联想 ThinkPad X1 Fold(均尚未正式发布)。

至于大家关心的这种“三明治”设计结构的散热挑战,鉴于 Lakefield 走的是经济路线,想必也不会由太大的问题。