新光刻技术:交替堆叠沉积

总之,3D NAND和现有平面NAND表现出了极大背离。在2D NAND中,它的制程是依赖于高级光刻技术。虽然3D NAND制程中采用了后缘40纳米到20纳米的设计规格。光刻技术仍在使用,但它不再是最关键的环节。因此对于3D NAND,所面临的挑战从光刻技术转向沉积和刻蚀。

实际上,3D NAND面向半导体行业推出了许多极具挑战性的新式制程步骤。“通过将位串迁到三维空间,该技术让许多图形微缩的挑战难度降低不少,” Coventor首席技术官David Fried表示。“但它已经推出了一些相当复杂的新制程。这些制程的均一性(即制程能力)是关键。所以在我看来,挑战主要集中在了一些关键制程的可变性控制上。”

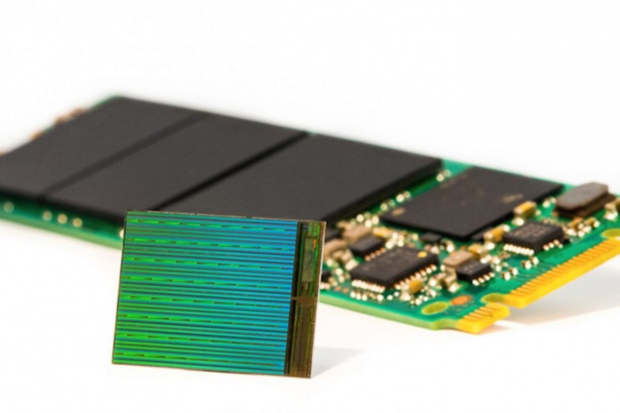

3D NAND流程从一个衬底开始。那么供应商开始经历流程中的第一个巨大挑战——交替堆栈沉积。采用化学气相沉积(CVD),交替堆栈沉积包含了一个在衬底上逐层沉积并堆叠薄膜层的制程。

这个制程更像是做夹心蛋糕。简而言之,一个材料层沉积到衬底上,然后有一个材料层再罗列上去。这个进程数次重复,直到设备达到想要的层数。

Objective Analysis称,每一个供应商用于生产3D NAND设备,所构建堆叠层的使用材料不同,三星在衬底上沉积氮化硅和二氧化硅的交替层。相比之下,东芝的3D NAND技术则采用了导电的多晶硅和绝缘的二氧化硅这两个交替层。

Ping称,交替堆叠沉积必须要对良好的均一性和低缺陷率进行精确控制。“首先,均一性必须要好,一切都要回归到压力控制,因为交替的薄膜材料不同。每一层薄膜都可能会存在不匹配问题,压力能够显示出来。”

这些挑战随着供应商设备层数的增高而不断加大。“每一个步骤的重复也是至关重要,而且为了控制成本它必须要做到高产能率。”泛林半导体公司的Pan如是说。

高纵横比刻蚀

交替堆叠沉积的步骤之后,一层硬掩膜(hard mask)放置在表面,然后依照图案在上面开孔。接下来整个流程最难的部分来了——高纵横比刻蚀。

从设备的顶部到衬底刻蚀微小的槽位或通道。为了证明该步骤的复杂度举例——三星的3D NAND设备在同一芯片上刻蚀了250万条微小的通道。每一条通道都必须要并行统一。

现在的高纵横比刻蚀技术能够处理32-48层设备的需求。对于这些芯片,纵横比范围在30:1到40:1。“这种刻蚀技术相当复杂。均一性对存储设备的性能至关重要,” Fried表示。这项统计也是极为惊人的。一旦刻蚀完成,内部开孔的数量也是不容小觑。

那么问题?目前的高纵横比刻蚀工具要么未就绪,要么在设法满足64层及以上设备的需求,纵横比范围为60:1到70:1。Ping称:“以目前的刻蚀能力而言太高了。刻蚀和硬掩膜技术还未必可用于60:1或70:1纵横比。”

再往前,NAND供应商双管齐下。第一根管,它们要等新一代高纵横比刻蚀工具等技术的到来。然后,给够时间准备刻蚀机,它们可能会微缩到——32层和48层,再到64层,96层,然后128层。

第二根管,NAND供应商将会开发新一代string stacking技术。(详见下文)

电荷捕获VS浮栅

在转向string stacking技术之前,供应商继续微缩现有3D NAND。除了沉积和刻蚀,现有3D NAND还进行了其它复杂的步骤,其中包括浮栅的形成。

对于这个,行业转向两个选择方向。三星,海力士和闪迪/东芝二人组都利用电荷捕获闪存技术。这项技术采用了非导体氮化硅层,这个层环绕一个单元的控制栅,后者转而捕获电荷保持单元完整性。

相比之下,英特尔/美光二人组未采用电荷捕获的方式,而是扩展浮栅结构至3D NAND。“在浮栅中,这个栅实际上是导体,一个电荷捕获层其实类似一个浮栅,是一个绝缘体。” Objective Analysis公司Handy如是说。

浮栅设计一些繁杂的图形步骤。“把图形刻印在一个垂直孔的面上实在很难。你必须要经过很多复杂制程。” Handy补充道。

当然,电荷捕获也有弊端。“电荷捕获的优势是你不必刻印图形,它在这方面更容易,但除了三星之外,其它厂商无法有效控制电荷捕获的成本。”

金属沉积

如果开发了栅极,下一步依旧很难。设备需要连接。设备利用一种导体进行回填,使用了金属沉积法。

泛林半导体公司高级副总裁兼首席技术官,Dave Hemker称,“金属沉积上所面临的一个挑战就是,我们看到很多客户‘用钨金属来回填’这是一种微妙的沉积法,因为你在做一个非视距(non-line-of-sight)沉积,事后难免得奔回去回填金属钨。如果你无法恰当处理这个制程,可能要预先放置前体(pre-cursor)然后析出钨粉回填。”

String stacking

在这个流程中,步骤把握难度都很大,但最大的挑战十分明确。即便业内解决了高纵横比刻蚀问题,现在的单字符串3D NAND技术也仍在约48层和/或64层打转。

就算刻蚀机也准备就绪,3D NAND也只能到达128层。Ping表示:“这是因为纵横比受到该制程的限制。因此你必须找一个解决方法绕过这些限制。”

答案为何?String stacking。在这个方法中,供应商将单个3D NAND设备堆叠起来。每一台设备可能被一个绝缘层隔开。“当你进行string stacking时,你就完成了一个字符串,接下来复制步骤环节也就畅通无阻了。” Ping如是说。

例如,一家供应商想开发一款48层设备。为了设计这样的芯片,需要进行同样的制程,就像交替层沉积,刻蚀等。

那么,这个供应商就得用相同的流程去开发一个不同的48层芯片。这个制程不限于48层的芯片。它也可能堆叠多个32层芯片。如果这项技术可用,那么它还可以堆叠64层,96层甚至128层设备。

虽然理论上供应商可能会选择用32层和48层进行string stacking。因为相比96层或128层芯片,开发单个32层或48层的设备的压力限制较小。

Ping继续表示,不过很说到底3D NAND采用string stacking也只是能达到堆叠近300层。“然后就会出现问题。你堆叠的时候,成品率损失持续增长,这就会成为限制。再加上,一切受压力所限。如果你放太多的膜,那么压力也会出现限制。”

然而,供应商会如何在string stack上将单个3D NAND设备连接在一起尚有待观察。对于这个问题,行业的互联方案可以说是五花八门。“你会有4到5个不同的选择。你可以在中间构建一个共享位线。另一个选择则是构建一个字符串,然后与每一个字符串直接连接。”

string stacking的确有很多不确定性和挑战。可即便没有string stacking,行业也在面临一些挑战。不论如何,行业必须掌握和完善3D NAND不同的制作步骤。否则,这项技术成本会继续昂贵下去,至少对绝大多数OEM而言。